ANZINE : CAE 기술 매거진

이전 ANZINE Home Tech-Insight

End-to-End Interconnect Co-simulation with “optiSLang”

- 이강표 매니저

- 태성에스엔이

- kplee@tsne.co.kr

End-to-End Interconnect Co-simulation with “optiSLang”

Introduction

서론

Ansys optiSLang®은 CAE 프로세스를 자동화하고 설계 최적화를 수행할 수 있는 강력한 소프트웨어 플랫폼이다. 이 프로그램은 다양한 엔지니어링 분야에서 활용되고 있으며, 최근 도입된 AI+ 기능을 통해 인공지능과 머신러닝을 활용하여 복잡한 설계 문제를 해결하고 다양한 솔루션을 도출하는 데 탁월한 성능을 제공한다.

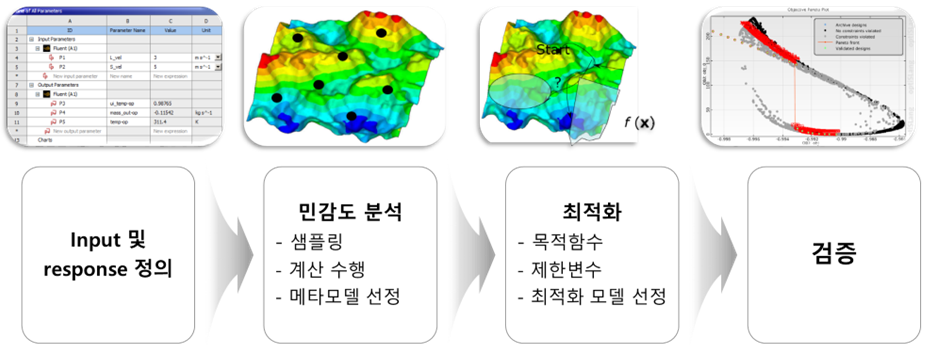

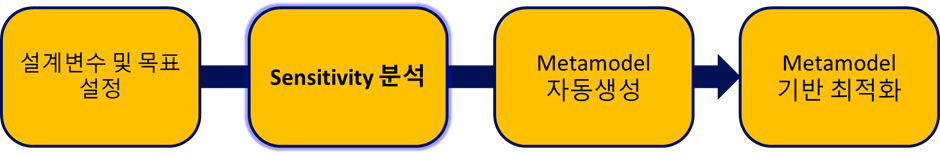

[그림 1] 최적화 프로세스

[그림 1]과 같이 이 프로그램은 PIDO (Process Integration Design Optimization) Tool로 Process Integration은 시뮬레이션 과정을 자동화하는 방식을 의미하며, Design Optimization은 설계를 이해하고 기존대비 향상한 제품 설계를 할 수 있도록 도와주는 최적화 프로그램이다.

최적화를 수행하기 위해 위와 같은 단계로 진행한다. 첫 번째, 설계변수인 Input과 설계의 성능을 평가하는 Response를 설정한다. 두 번째, 민감도 분석에서 샘플링 개수를 설정하고 해석으로 계산된 결과값을 얻는다. 이를 바탕으로 Surrogate Model을 만들면 제품의 전반적인 이해를 도모할 수 있고 Response가 크게 변화는 영향력이 큰 설계변수를 확인할 수 있다. 세 번째, 최적화 단계에서는 Response로 설정했던 값을 목적함수와 제한변수로 최적화 목적에 따라 나누고 앞서 설정했던 surrogate model을 기반으로 최적화 모델을 선정하여 최적화를 수행한다. 목적함수는 최대/최소와 같은 최적화하고자 하는 대상을 수학적으로 표현하고 제한변수는 최적화 문제에서 고려해야 할 제약 조건을 나타내는 변수다.

본론

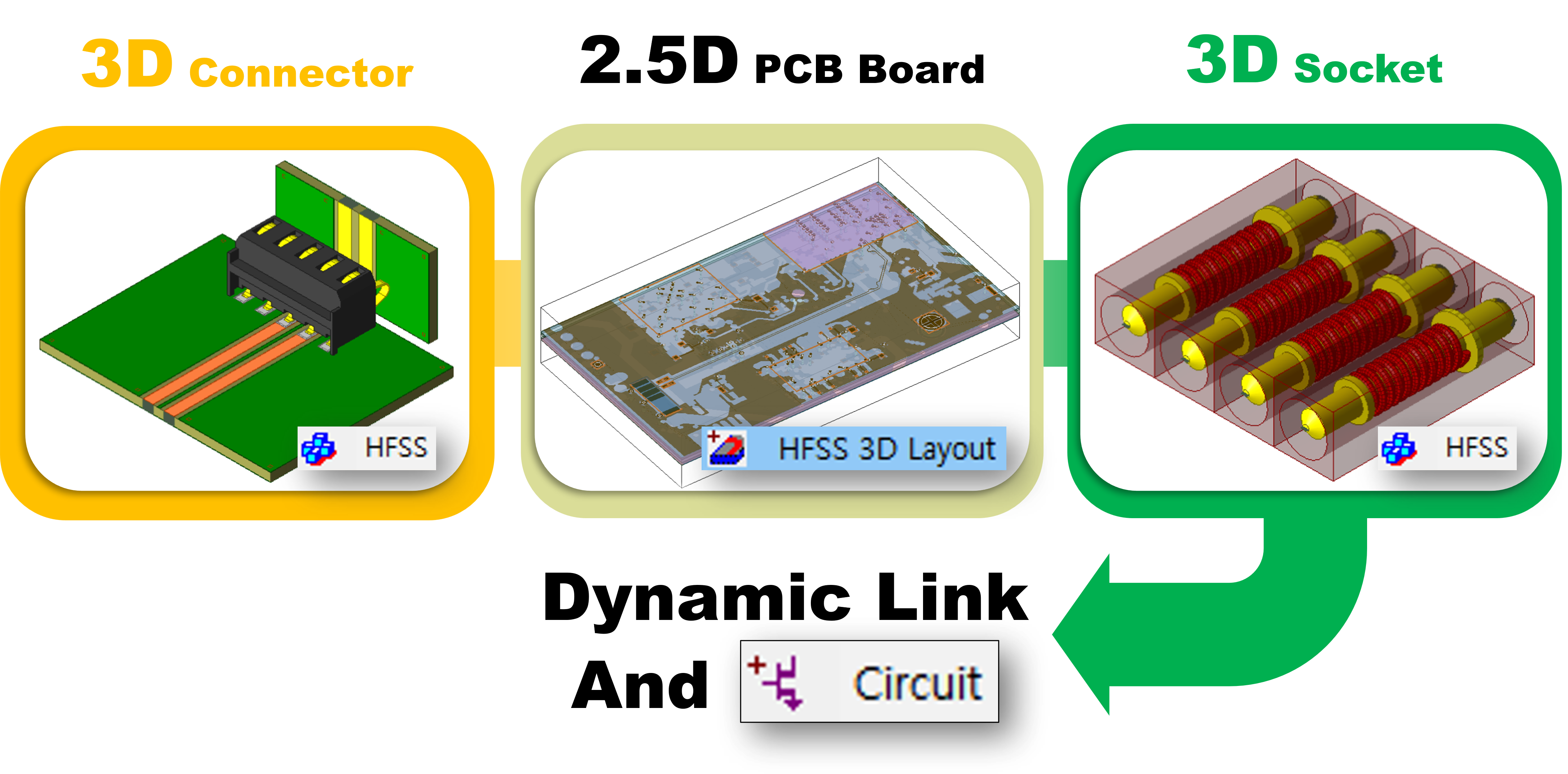

커넥터와 소켓은 3D 모델링이기 때문에 HFSS로 해석하고 PCB Board는 2.5D ECAD파일로 해석해야 속도 및 리소스에 유리하기 때문에 HFSS 3D Layout으로 시뮬레이션 수행하였다. [그림 2]와 같이 순서대로 연결시켜서 해석하기 위해서는 Dynamic Link 기능을 사용해서 Circuit에 구현해야 End-to-End Interconnect 분석이 가능하다.

[그림 2] Design Overview

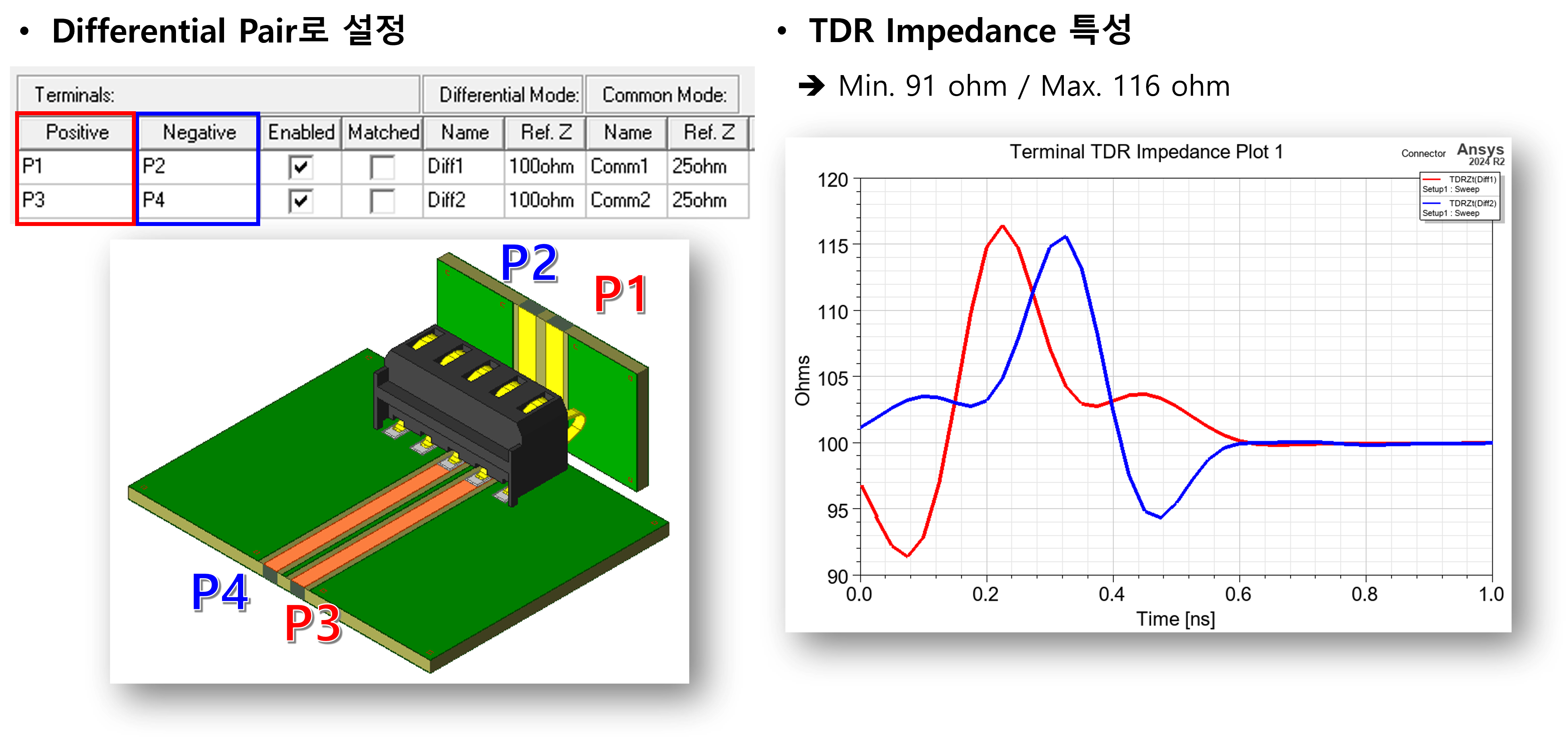

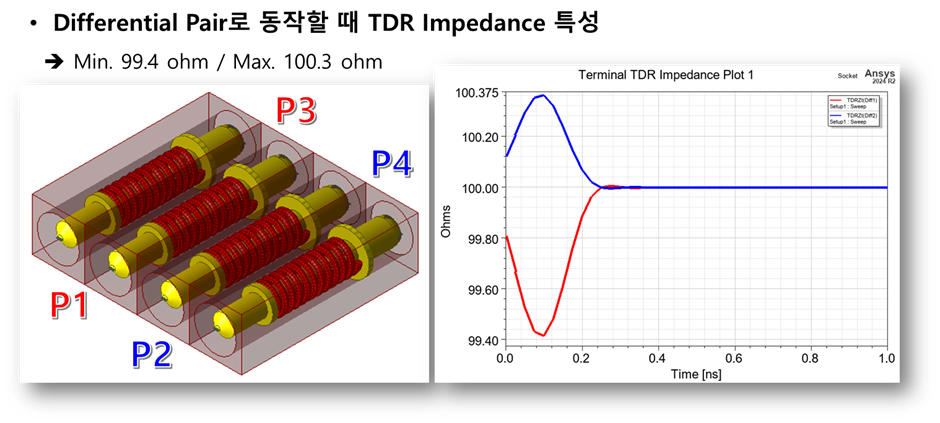

Differential Pair로 동작하는 것을 가정하여 Port P1, P3는 Positive, P2, P4는 Negative로 설정한다. 관심 주파수는 0-8GHz에서 801point로 지정하여 분석에 대한 신뢰도를 높였고, [그림 3]에 표시한 것처럼 Port는 빨간색과 파란색으로 식별하였다. 해석 결과 커넥터의 TDR 특성은 Max/Min 차이가 25ohm 이상 발생했다.

[그림 3] Connector Simulation[HFSS]

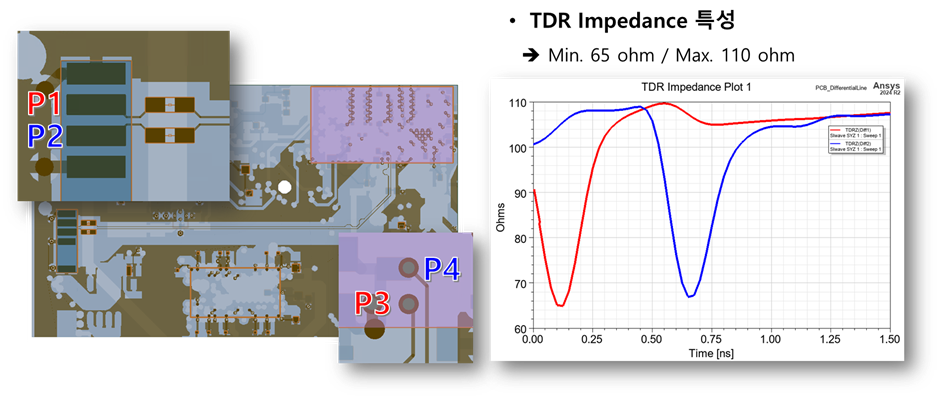

[그림 4]는 PCB Board를 3D layout으로 해석 하였으며, Excitations, Differential Pair, Solution and Frequency Sweeps 설정은 동일하다. TDR 특성은 45ohm으로 큰 차이를 보였다.

[그림 4] PCB Board Simulation [3D Layout]

Socket은 길이가 짧아 TDR 특성이 크게 변하지 않기에 변수 지정은 하지 않았다. [그림 5]

[그림 5] Socket Simulation [HFSS]

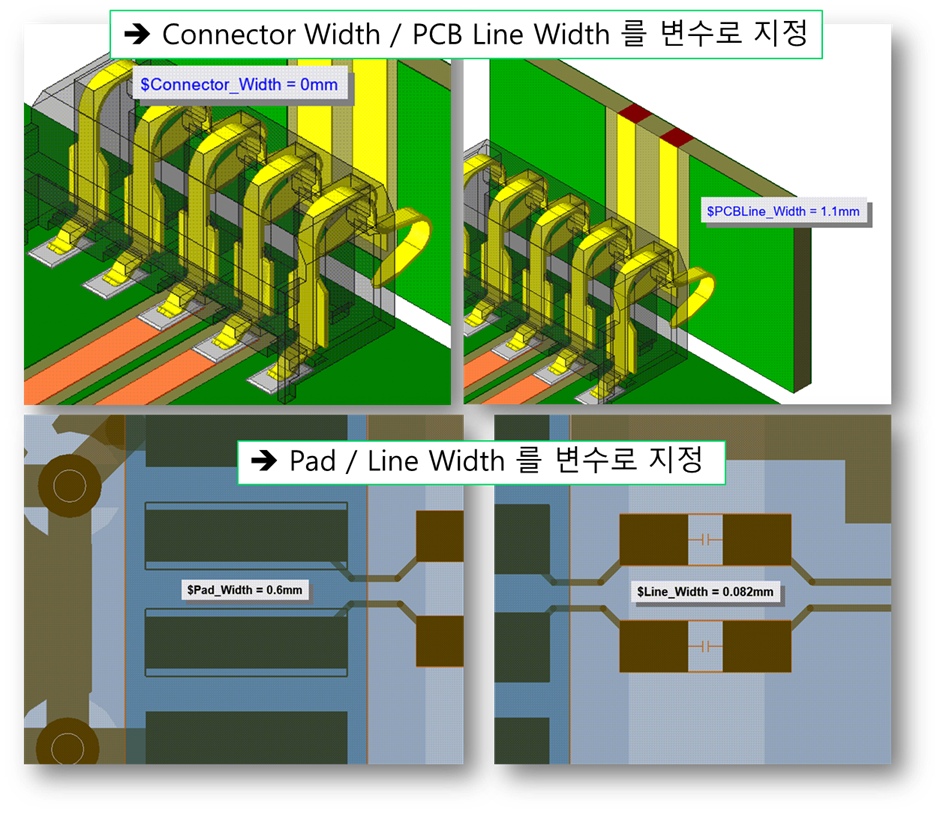

사용자는 TDR 특성을 최적화하기 위해 Connector에서는 Pin의 Width와 PCB Line Width를 변수로 지정하고, PCB Board에서는 Pad와 Line의 Width를 변수로 지정하였다. [그림 6]

[그림 6] 변수 설정된 모델링

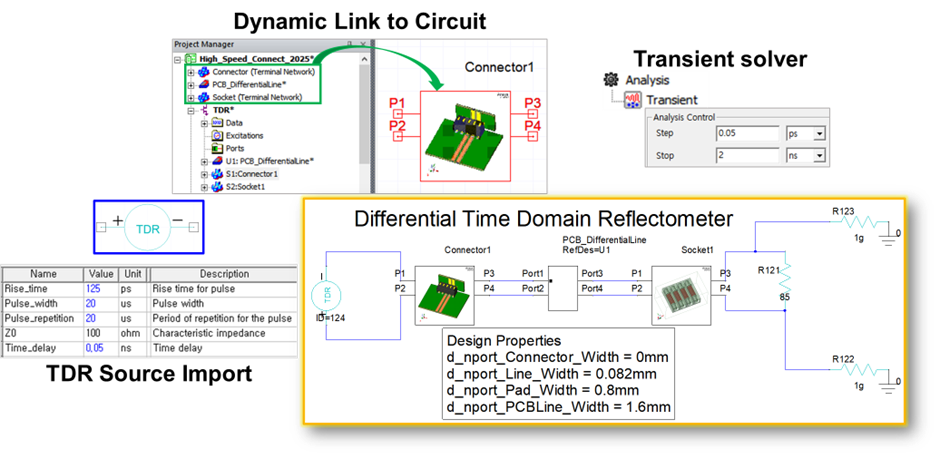

각각의 컴포넌트들을 결합해서 해석하기 위해 Circuit으로 [그림 7]과 같이 회로를 구성합니다. TDR 특성을 보기위한 Source 정보를 입력해 주고, 각 컴포넌트들을 Circuit 회로 도면 위로 Drag & Drop 하여 Dynamic Link 시켰다. 각각의 컴포넌트들을 결합해서 해석하기 위해 Circuit으로 [그림 7]과 같이 회로를 구성합니다. TDR 특성을 보기위한 Source 정보를 입력해 주고, 각 컴포넌트들을 Circuit 회로 도면 위로 Drag & Drop 하여 Dynamic Link 시켰다.

[그림 7] 디자인 결합을 위한 Circuit 회로 구성

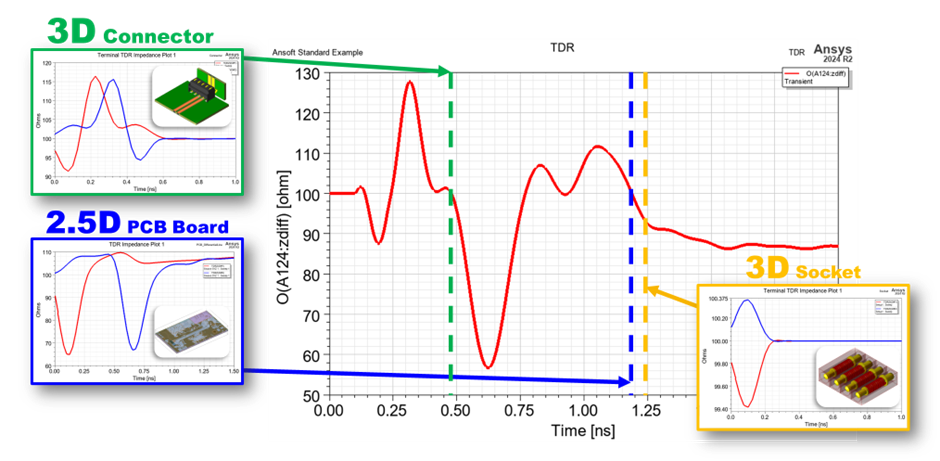

결합 완료 후 Transient 해석하면 각 컴포넌트 결과를 합쳐서 연결된 TDR 그래프를 도출할 수 있다. [그림 8] 일반적인 Diff. Line이라면 100ohm으로 일정해야 성능 저하가 발생하지 않기 때문에 optiSLang을 활용한 최적화로 최대한 결과 그래프를 평탄하게 해줘야 한다.

[그림 8] Full TDR Result

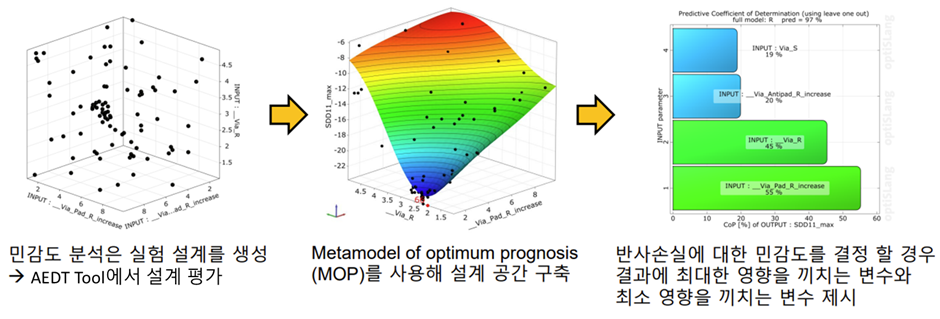

설계 변수 및 목표를 설정하였으니, optiSLang의 Sensitivity(민감도) 분석을 진행한다. 민감도 분석은 기본적으로 입력 변수를 Sweep 하여 목표성능을 극대화하는 입력 변수 조합을 찾는 작업이다. 이 민감도 분석을 이용해서 가상의 Metamodel을 구성하는데 이것을 이용하면 알아서 목표와 관련이 적은 변수를 배제하며, 목표달성과 연관성이 높은 설계변수와 범위를 자동으로 추출하여 빠르고 효율적인 최적화를 수행한다. [그림 9]

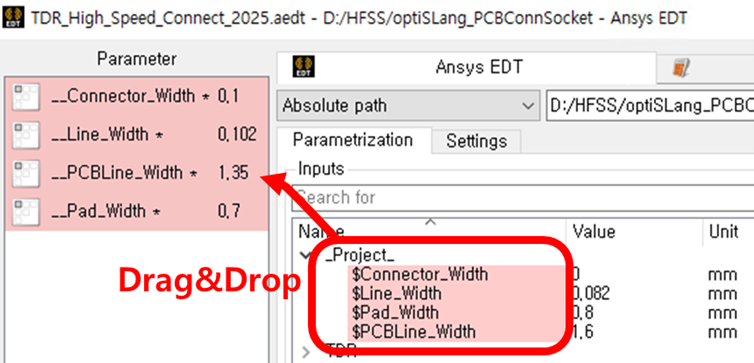

[그림 10]처럼 TDR 성능에 영향을 끼칠 것 같은 변수만 우선적으로 선정해 4개의 변수를 optiSLang 최적화 과정에 Drag&Drop으로 포함시킨다.

[그림 9] Sensitivity 분석 하는 이유

[그림 10] Sensitivity 해석 설정 - 최적화 변수 설정

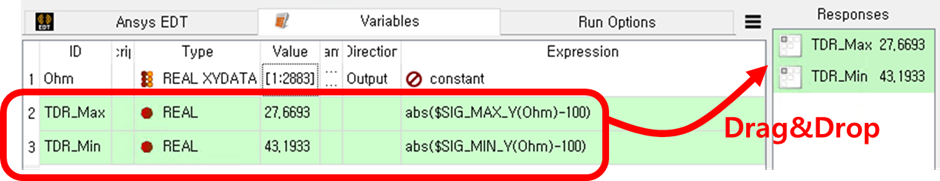

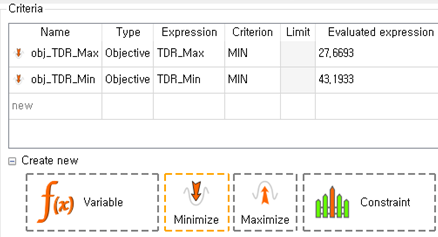

TDR 구간 중 가장 높고 낮은 임피던스를 갖는 Max./Min. 구간을 타겟으로 100ohm을 만족하게끔 [그림 11]의 Variables 탭에서 abs 수식을 활용해 TDR 값 계산하고 Reponses 항목으로 Import 시킨다. [그림 12]와 같이 계산된 값을 Minimize 기준을 적용하면 두 값이 0에 수렴하면서 결과적으로 선로의 임피던스를 100ohm에 맞추는 과정이다.

[그림 11] Sensitivity 해석 설정 – 최적화 목표 설정

[그림 12] Sensitivity 해석 설정 - Criteria

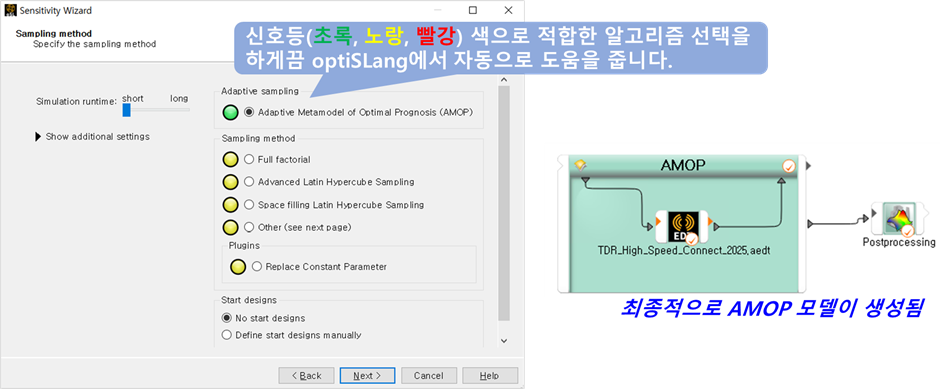

optiSLang은 [그림 13]처럼 Wizard 방식을 지향하고 있어서 사용자가 최적화에 관한 알고리즘을 모두 알고 있지 않더라도 자동으로 적합한 알고리즘 선택을 하게끔 신호등(초록, 노랑, 빨강) 색상으로 가이드를 제공하여 사용자의 편의성을 높였다. 이후 설정을 완료하면 AMOP 모델이 생성되고 그 옆에 후처리 아이콘이 연결됩니다.

[그림 13] Sensitivity 해석 설정 - 알고리즘 선택

[그림 14]의 최적화 Flow에서 optiSLang은 추가적인 Simulation 없이 입력 변수에 따른 성능을 예측할 수 있는 일종의 ROM 또는 Behavior Model, 즉 Metamodel을 자동으로 생성해주며, 이렇게 생성된 Metamodel을 AMOP(Adaptive Metamodel of Optimal Prognosis)라고 부릅니다.

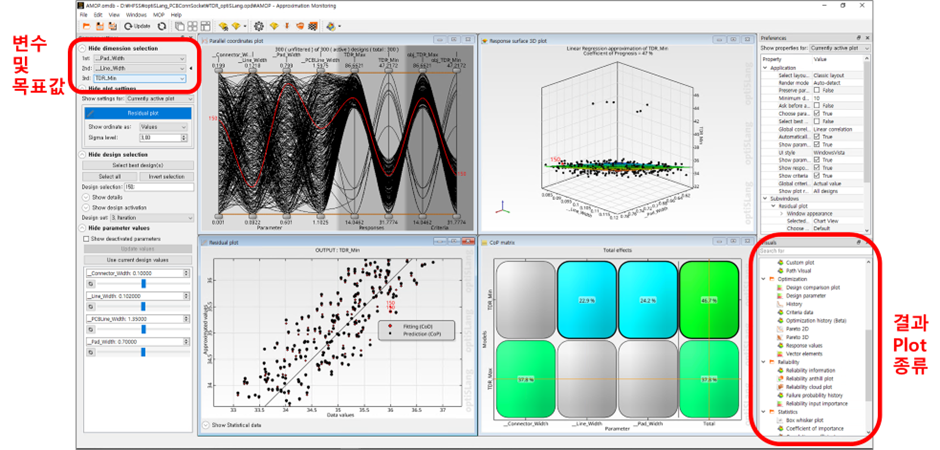

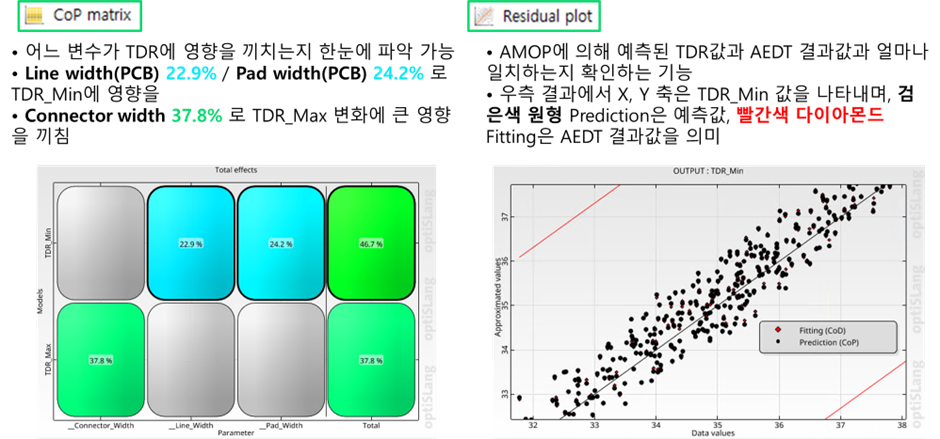

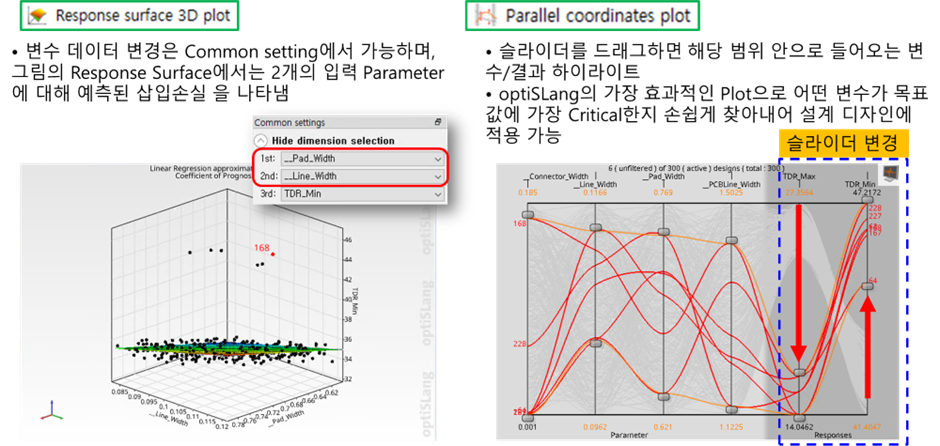

[그림 17]은 Response Surface 3D Plot과 Parallel Coordinates Plot을 활용하여 설계 변수 변화에 따른 TDR_Max./Min. 응답 특성을 시각적으로 분석한 결과를 나타낸다. Response Surface Plot을 통해 Pad Width와 Line Width 변화에 따른 응답 경향을 확인하였으며, Parallel Coordinates Plot에서는 슬라이더를 이용하여 목표 응답을 만족하는 설계 변수 조합을 효과적으로 탐색할 수 있음을 확인하였다.

결론

본 연구에서는 Ansys HFSS, HFSS 3D Layout, Circuit 환경을 연계한 End-to-End Interconnect 해석을 수행하고, optiSLang을 활용한 민감도 분석 및 메타모델 기반 최적화를 통해 Differential Line의 TDR 임피던스 특성을 개선하였다. 특히 CoP 분석을 통해 Pad Width가 가장 큰 영향도를 가지는 주요 설계 변수임을 확인하였으며, Response Surface 및 Parallel Coordinates 분석을 통해 설계 변수 변화에 따른 응답 특성과 최적 설계 영역을 직관적으로 파악할 수 있었다. 이러한 결과를 통해 optiSLang 기반 설계 최적화 접근 방식이 복잡한 전기적 인터커넥트 구조에서도 효과적으로 활용될 수 있음을 확인하였다.

맺음말

최근 전자 시스템의 고속화와 고집적화가 진행됨에 따라 인터커넥트 구조에서 발생하는 신호 무결성 문제를 효과적으로 해결하는 설계 방법의 중요성이 더욱 커지고 있다. 본 연구에서 제시한 Ansys 기반 통합 해석 및 optiSLang을 활용한 설계 최적화 방법은 복잡한 시스템 환경에서도 설계 변수의 영향도를 체계적으로 분석하고 최적 설계를 도출할 수 있는 효율적인 접근 방법임을 보여주었다. 특히 메타모델 기반 최적화는 반복적인 시뮬레이션 부담을 줄이면서도 설계 공간을 효과적으로 탐색할 수 있다는 장점을 가지며, 실제 엔지니어링 설계 과정에서 설계 초기 단계의 의사결정을 지원하는 유용한 도구로 활용될 수 있다. 향후 이러한 방법론은 다양한 전자 패키징 및 고속 인터커넥트 설계 문제에도 확장 적용될 수 있을 것으로 기대된다.

㈜태성에스엔이

㈜태성에스엔이